Summary

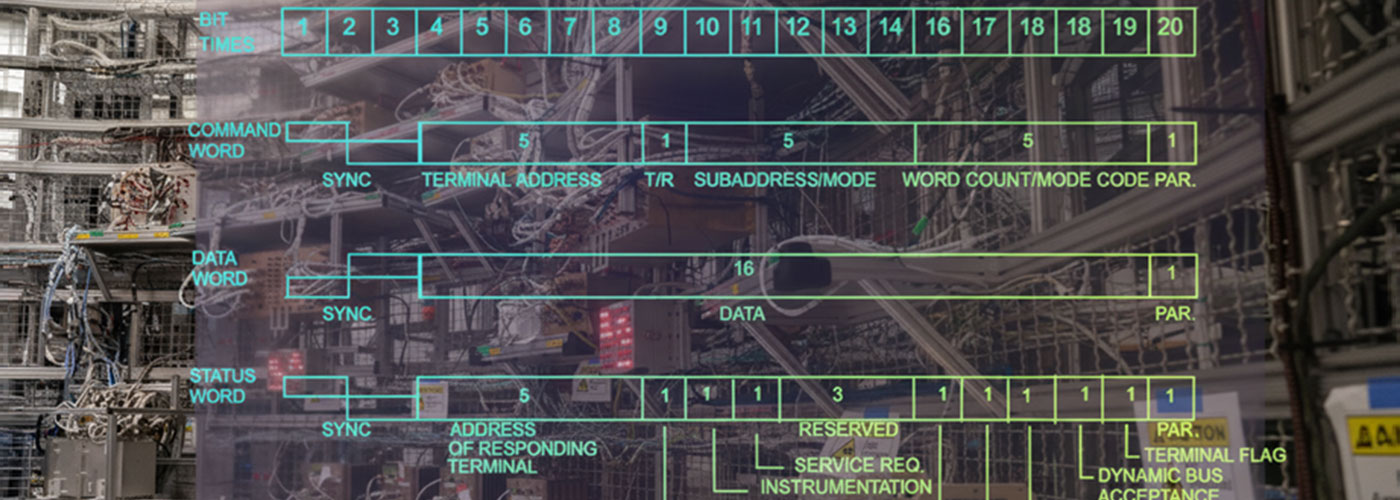

Hardware-in-the-loop (HIL) and production validation tests often rely on precise, deterministic sequencing to ensure that every stimulus, measurement, and control action occurs with exact timing. NI VeriStand’s real-time sequences (.nivsseq files) are widely used for this purpose, offering microsecond-level deterministic control on PXI and CompactRIO targets.

While the Real-Time Sequence Editor provides a powerful interface, managing hundreds of variations across complex test systems can be time-consuming and error-prone. For DMC’s recent NASA BOLE project, we built a solution that leverages the VeriStand .NET API to programmatically generate deterministic sequences, giving engineers a feature-rich editing experience and dramatically reducing the time required to build, modify, and deploy sequences.

Customer Benefits

- Time Savings – creating a new sequence goes down from 30-60 minutes of manual work to 1-5 minutes, with automatic updates for time from t0 and message parameters eliminating repeated manual labor when something changes

- Scalability – updating timing parameters across multiple sequences can be done in a single configuration update instead of manual edits to each file

- Automated Error Checking – debugging syntax or dependency errors are done via automated validation with the .NET API, reducing the number of human errors in test sequences with clear analysis

- Customization & Ease of Use – each step has a clear configuration UI, and is tailored to the specific needs of the project

- Deterministic Control & Timing Visibility – the sequences run deterministically on Real Time targets, with sequence steps automatically updating with their relationship to t0 at they are dragged-and-dropped to different locations in the test

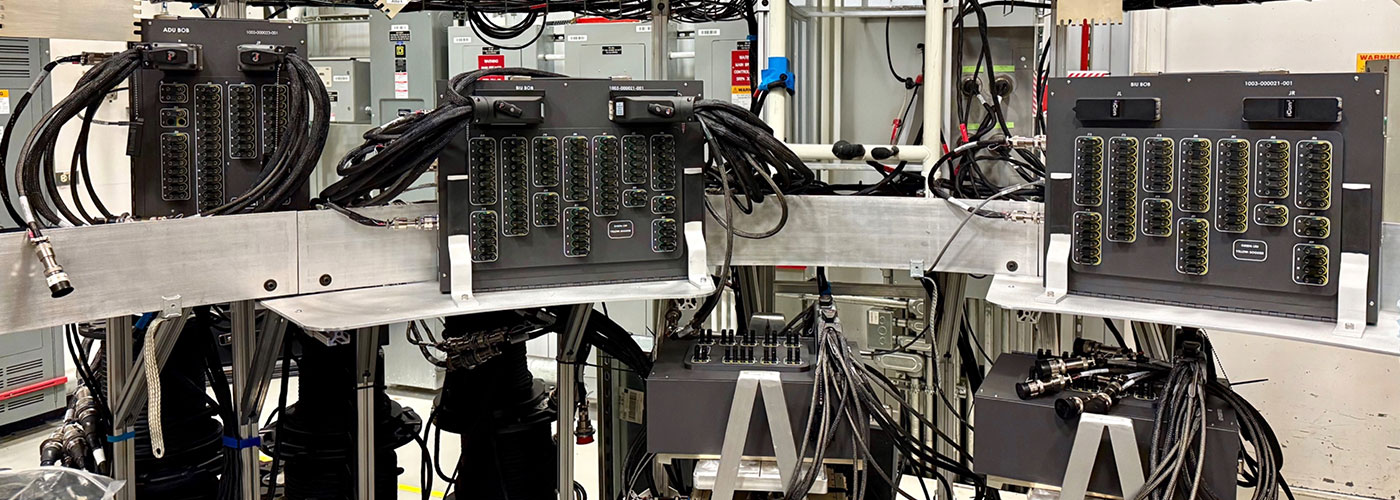

Technologies (Hardware & Software)

- NI LabVIEW

- NI VeriSTand

- .NET API

Solution

Technical Challenges

In traditional workflows, engineers would manually create or edit .nivsseq files using VeriStand’s sequence editor. For small projects, this is manageable, but as test systems grow in complexity, this approach becomes a bottleneck. Customer teams face several challenges:

- Repetitive manual editing: Each new test variant requires copying, renaming, and modifying sequences, which introduces risk for human error.

- Limited scalability: Updating timing parameters or channel references across dozens of sequences is tedious and prone to mistakes.

- Fragmented version control: XML-based sequence files are not easy to diff or merge, making collaboration difficult.

- Difficulty integrating with automation pipelines: Generating sequences dynamically from configuration data or test templates is cumbersome without programmatic support.

Test engineers needed a workflow that preserves VeriStand’s deterministic execution while introducing modern software practices: automation, templates, and easy maintainability.

Test engineers needed a workflow that preserves VeriStand’s deterministic execution while introducing modern software practices: automation, templates, and easy maintainability.

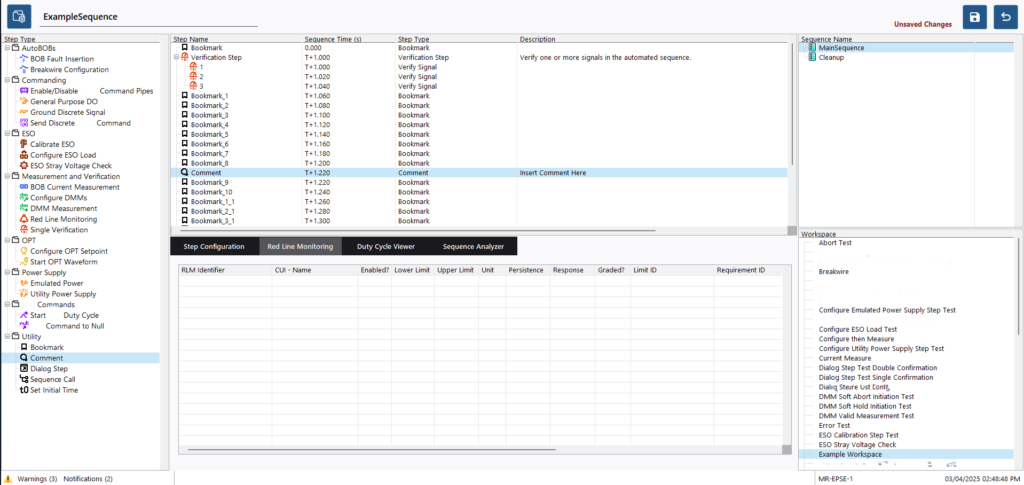

Feature-Rich Editing Experience

One of the most important customer benefits of the NASA SLS BOLE sequence editor is the enhanced editing experience. Unlike manually editing .nivsseq XML or using the built-in editor alone, our system provides:

- Inline expressions and syntax highlighting for VeriStand commands, channel references, and arithmetic operations.

- Drag-and-drop building blocks for common actions such as setting channels, waiting, calling sub-sequences, or logging data.

- Parameter linking to external configuration files, calibration databases, or spreadsheets, allowing sequences to adapt automatically to different DUTs or testing needs.

- Live preview of the generated

.nivsseqfile, so engineers can validate sequence structure before deployment. - Version control integration, enabling teams to track changes, perform diffs, and maintain collaboration with confidence.

This richer interface allows engineers to focus on test logic and system design rather than tedious XML editing or maintenance of sequences. The above screenshot from our internal editor illustrates the intuitive workflow: variables are defined once, building blocks are assembled visually, and the generated sequence remains fully compatible with VeriStand’s real-time engine. The customer therefore has been able to make updates much faster than they otherwise would have with less headache, all with the same deterministic results that VeriStand provides.

Backend Architecture

Our team developed a custom sequence generation system built on the VeriStand .NET API (NationalInstruments.VeriStand.RealTimeSequenceDefinitionApi). This approach allows engineers to define sequences programmatically and deploy them to the real-time target without manually editing XML files.

Key components of the solution include:

- Sequence Generator Application: A Windows-based tool that reads configuration files or test templates and constructs sequences automatically.

- VeriStand Real-Time Target: A PXIe or CompactRIO controller that executes the generated sequences deterministically.

- Integration Layer (Optional): Host-side triggers and monitoring via TestStand or the VeriStand Gateway API, enabling fully automated test execution.

By generating sequences dynamically, engineers can maintain a single source of truth for logic and parameters, eliminating repetitive editing and minimizing human error.

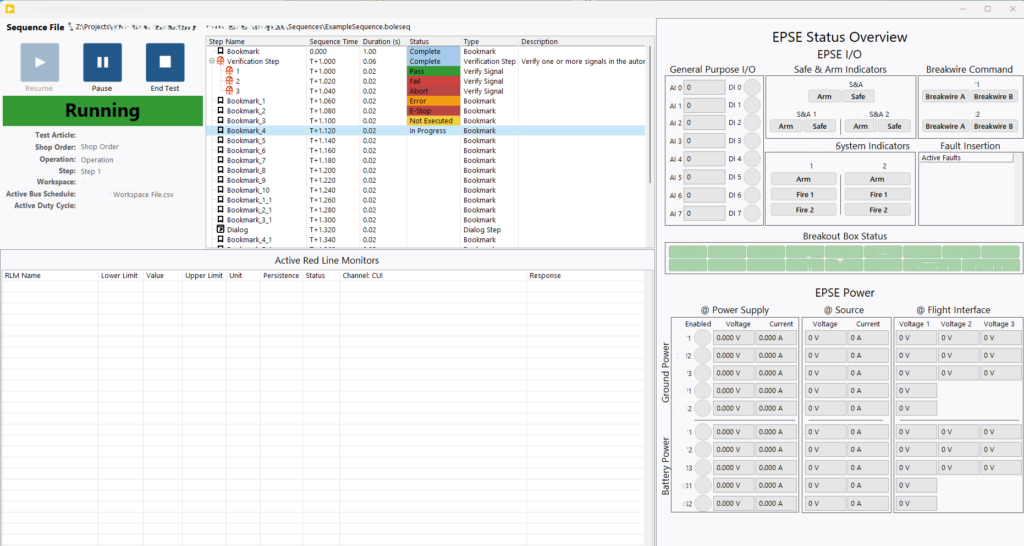

Visualization

The sequence editing experience isn’t the only benefit to the custom sequencing portion of DMC’s application: when running tests, our client gets a full view of the sequence step results, timing, as well as live data for specified parameters. DMC’s main goal with the software architecture for this project was to give our client an easy and clear user interface/user experience. Many standard aerospace HIL systems are deterministic and detailed, but are confusing, dated, and cumbersome when put into use. DMC’s sequence overview screen, as shown below, gives the user a clear picture of sequence step status, custom alarmed channels, and live LRU status data on top of the timing reliability.

Learn more about DMC’s Test & Measurement HIL expertise and contact us for your next project.

Additional Parts to this Project

Learn more about the other phases of this project’s success.